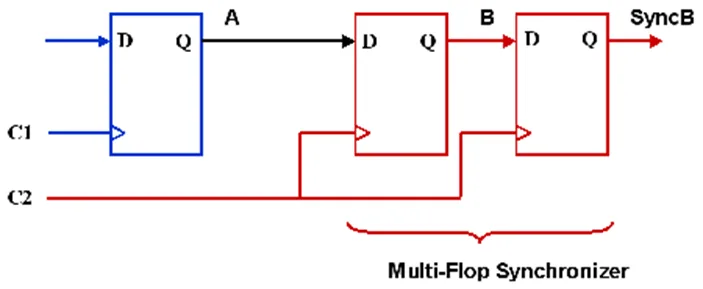

oThey are used when signal crosses asynchronous clock domains.

Sync Flop added between two flops operating on asynchronous clocks to avoid metastability.

The main responsibility of a synchronizer is to allow sufficient time such that any meta-sable output can settle down to a stable value in the destination clock domain.

Generally 2 stage synchronizer is sufficient to remove all likely meta-stability.

Sync flops operating on destination clock domain.

the first flip-flop samples the asynchronous input signal into the destination clock domain.

Second stage waits for a full destination clock cycle to permit any meta-stability on the stage-1 output signal to decay,

then the stage-1 signal is sampled by the same clock into a second stage flip-flop, with the intended goal that the stage-2 signal is now a stable and valid signal synchronized into the destination clock domain

Generally no combo logic is prefered in RTL between two asynchronous flops.