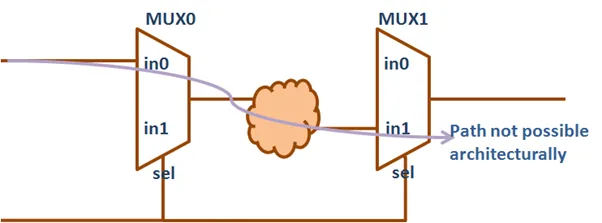

oFalse Path (set_false_path):

Specific path between a startpoint and endpoint cannot be logically sensitized during normal circuit operation. Although a physical path exists, signals will never actually propagate from the startpoint to the endpoint along that path under functional conditions

STA Action: The tool completely ignores this path for all timing analysis (setup, hold, DRCs). It assumes the path has infinite time to propagate.

When to Use: Only for paths that are guaranteed to be functionally impossible or irrelevant to the timing modes being analyzed.

Common uses: between asynchronous clock domains (after synchronizers), paths related to test logic disabled in functional mode, static configuration paths.

Multicycle Path (set_multicycle_path):

Meaning: data launched from the startpoint is allowed more than one clock cycle of the destination clock to arrive and be stable at the endpoint.

STA Action: The tool modifies the setup and hold check edges:

set_multicycle_path <N> -setup: Moves the setup check edge N clock cycles later.

set_multicycle_path <N-1> -hold: Moves the hold check edge (N-1) cycles later (relative to the default hold edge, which is 0 cycles after launch).

Optimization Impact: Synthesis and PnR tools will still optimize the path, but against the relaxed (multicycle) setup constraint.

When to Use: For paths intentionally designed to take multiple clock cycles, often involving slow logic, calculations spanning multiple cycles controlled by enables, or certain CDC paths

- Key Difference: False paths are ignored by timing analysis and optimization. Multicycle paths are analyzed and optimized, but against modified setup/hold timing requirements